## <u>Programma di ricerca e sviluppo tecnologico volto alla produzione di</u> strumentazione scientifica, attinente al settore "Strumentazione Scientifica"

#### Consuntivo scientifico del primo anno di attivita'

Il "Programma di ricerca e sviluppo tecnologico volto alla produzione di strumentazione scientifica", attinente al settore "Strumentazione Scientifica" del Fondo 5%, si articola secondo le seguenti sei Linee di Ricerca:

- 1) Rivelatori al silicio con microelettrodi;

- 2) Microconnessioni verticali ad alta densita' (Bump Bonding);

- 3) Rivelatori di particelle ionizzanti a microelettrodi in gas (MSGC);

- 4) Front-end, lettura e trigger per lo spettrometro u di ATLAS;

- 5) Alimentatori per alte tensioni continue;

- 6) Sviluppo dell'elettronica di lettura per una camera a proiezione temporale ad argon liquido (ICARUS).

L'accordo di Programma MURST-INFN, stipulato il 16 marzo 1998, ha iniziato ad avere efficacia dalla data di registrazione, avvenuta nel mese di giugno dello stesso anno.

Va tuttavia osservato che la definizione del progetto di ricerca e' avvenuta molto prima della stipula dell'accordo. La approvazione da parte del CNST e' avvenuta nel novembre 1996 e la presentazione al MURST del programma definitivo nel giugno 1997. Dato che le sei linee sopra elencate sono strettamente legate ad attivita' di ricerca autonomamente perseguite dall'INFN, quali la sperimentazione all'acceleratore LHC al CERN di Ginevra e la sperimentazione presso il laboratorio Nazionale del Gran Sasso, e sono quindi vincolate a scadenze temporali indipendenti dal presente programma, si e' reso necessario non attendere la formalizzazione dell'accordo per dare l'avvio alle attivita' di studio, che sono iniziate essenzialmente a partire dal settembre 1997. Questo e' stato possibile utilizzando risorse messe a disposizione dall'INFN e dalle ditte coinvolte nei progetti, in attesa della disponibilita' dei finanziamenti di fonte MURST, ed ha richiesto in qualche caso una rimodulazione temporale delle differenti fasi dei progetti.

Per quanto detto sopra, il presente rapporto descrive i risultati conseguiti nell'effettuazione del programma a partire dall'inizio effettivo dell'attivita' fino all'estate (giugno) 1999. Come risulta dal seguito, l'avanzamento del progetto in tutte le linee di ricerca segue nella sostanza quanto previsto nell'accordo. In nessun caso vi sono indicazioni di problemi o difficolta' che possano portare ad una ridefinizione degli obbiettivi.

#### Rivelatori al silicio con microelettrodi (ditta ST Microelectronics)

Lo scopo di questa parte del programma e' di mettere a punto presso l'industria italiana la tecnologia per la produzione dei rivelatori a microstrisce di silicio che equipaggiano i grossi sistemi di tracciatura degli esperimento di LHC, in particolare il tracciatore centrale di CMS.

Le fasi di lavoro previste in sede di stesura del progetto erano le seguenti:

- I. Definizione di una tecnologia compatibile con le esigenze degli esperimenti a LHC e con le attrezzature presenti nell'industria; eventuali modifiche per la produzione di alcune serie di dispositivi semplificati; produzione e test di dispositivi completi.

- II. Produzione di una preserie per i vari tipi di dispositivi previsti per gli esperimenti di LHC, per qualificare i processi di produzione di larga scala.

# I. Definizione della tecnologia. (1997-2000)

La produzione di rivelatori al silicio richiede la realizzazione di giunzioni impiantate organizzate in microelettrodi, di lunghezza 6-12 cm e passo  $50\text{-}200~\mu m$  su dispositivi di grande area ( $40\text{-}90~\text{cm}^2$ ). L'array di giunzioni va realizzato su substrati di silicio ad alta resistivita' da operare in condizioni di svuotamento totale di volume. Sono parte integrante della tecnologia l'integrazione di circuiti di polarizzazione riproducibili ed uniformi sull'intera superficie del wafer, la produzione di un array di condensatori di disaccoppiamento integri al 99% ed il raggiungimento di tensioni di rottura superiori a 500~V con correnti inverse nell'ordine dei  $10~\mu A$ .

In una prima fase del lavoro è stata definita una tecnologia compatibile con le attrezzature presenti all'interno della ST-Microelectronics spa. A tale scopo sono state realizzate serie di prototipi nella linea pilota a 5" dedicata allo sviluppo di prodotti di

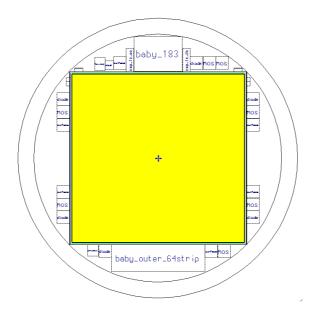

Fig. 1. Layout

R&D. In figura 1 e' illustrato il layout delle maschere disegnate presso l'INFN sezione di Pisa e realizzate presso la ST-Microelectronics.

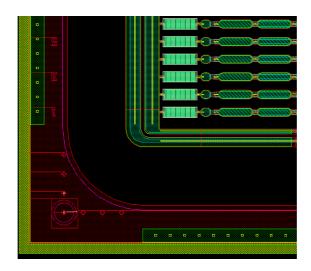

In figura 2 e' illustrato un dettaglio della regione di bordo del sensore con l'array delle strisce, le pad di microsaldatura, le resistenze in polisilicio usate per il bias delle strisce ed i markers di allineamento.

Fig. 2 Dettaglio del bordo di un rivelatore

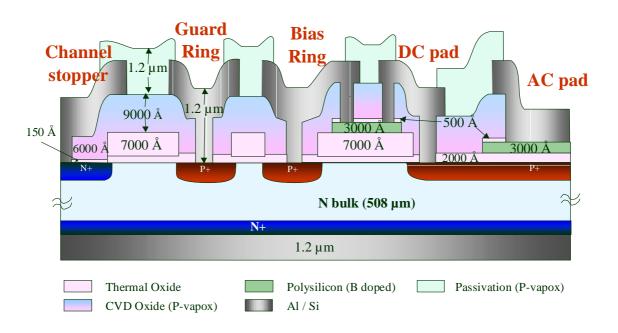

La tecnologia messa a punto per la realizzazione di questi dispositivi ha utilizzato i processi disponibili nella compagnia con una serie di varianti scelte per ottimizzare la qualita' complessiva dei dispositivi. In figura 3 e' mostrata una sezione trasversale del

dispositivo nella regione delle strisce con il dettaglio degli spessori degli ossidi usati per realizzare i condensatori di disaccoppiamento.

I principali risultati ottenuti con queste prime serie di prototipi su wafer a 5" sono la buona uniformita' nelle resistenze di polisilicio (meglio del 20% per valori intorno ad  $1.5~\mathrm{M}\Omega$ ), una resa dei condensatori discreta anche se non ancora ottimale (>95% in media per wafer), tensioni di breakdown superiori a 400V (un valore accettabile ma ancora al di sotto dell'obiettivo di progetto di avere rotture superiori a 500 V). In termini di corrente di leakage complessiva allo svuotamento queste prime serie di prototipi mostravano livelli di corrente inversa ragionevoli (intorno a 500 nA/cm² per dispositivi di circa  $40~\mathrm{cm}^2$ ).

Il programma successivo prevede il trasferimento della tecnologia finora messa a punto nella linea di R&D sulle linee di produzione standard, quindi su wafer da 6" e spessore 500  $\mu$ m. Allo stesso tempo saranno introdotti gli accorgimenti tecnici elaborati per migliorare le prestazioni sinora ottenute, con l'obbiettivo di raggiungere tutti i valori di progetto.

#### Microconnessioni verticali ad alta densita' (Bump Bonding) (ditta Alenia)

Lo scopo di questo programma e' di stabilire un metodo di produzione di moduli pixel con le caratteristiche richieste dall'eperimento ATLAS a LHC.

Un modulo pixel, nel caso dell' esperimento ATLAS, e' costituito da un sensore di silicio di  $\sim$ 2 x 6 cm<sup>2</sup> con circa 46000 connessioni a 16 chip di elettronica.

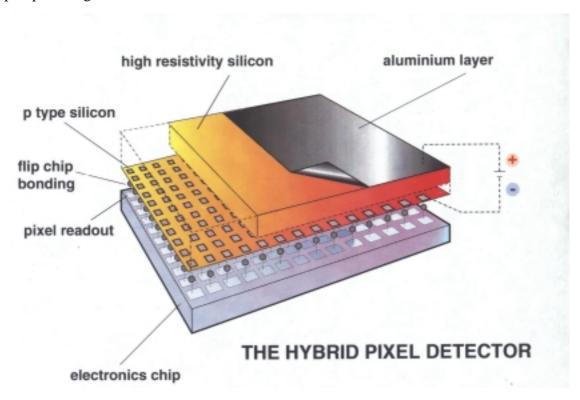

Per poter realizzare questo grande numero di connessioni su una piccola superficie, si ricorre alla tecnologia del flip-chip bonding . Questa tecnologia e' di uso corrente nell'industria elettronica nel caso di qualche centinaio di contatti per  ${\rm cm}^2$  e di un passo tra contatti superiore ai 300  $\mu m$ .

Questo programma di R&S si propone quindi di estendere la tecnolgia di circa 2 ordini di grandezza (in termini del numero di contatti per cm²) e di circa un ordine di grandezza per quanto riguarda la minima distanza tra i contatti.

La figura precedente illustra in maniera schematica come si presentano i componenti di un assieme connesso attraverso flip-chip bonding.

La maggior parte della superficie del sensore (high resistivity silicon) e dei chip di elettronica (pixel readout) e' coperta di isole di metallo a basso punto di fusione (bump), queste sono realizzate in indio e vengono depositate per evaporazione sotto vuoto attraverso maschere di precisione. La sovrapposizione precisa delle isole depositate sull'elettronica e di quelle depositate sul sensore e l'applicazione di una forza a

temperatura prossima ai 100 °C stabiliscono le connessioni elettriche in maniera permanente (flip-chip).

Ulteriori vincoli vengono dalla richiesta che i chip di elettronica debbano essere molto vicini l'un l'altro (per non perdere accettanza o risoluzione) e che si debbono trattare chip assottigliati fino a 150 µm (per ridurre il materiale inerte nell'apparato).

Il programma di lavoro e' dettagliato nella tabella seguente definita in accordo con il partner industriale scelto (Alenia Difesa), questa relazione copre i primi 15 mesi di lavoro, ovvero i punti da 1.1 a 1.6, escluso 1.4.

Nel corso di questo programma, e piu' precisamente l'11/1/1999, la Alenia Difesa ha cambiato ragione sociale in Alenia Marconi Systems (AMS), mantenendo pero' inalterato l'interesse e l'impegno sull' attivita' di bump-bonding.

| Obiettivi |                                             | 1 anno |  |  |  | 2 anno |   |  |  | 3 anno |   |  |  |

|-----------|---------------------------------------------|--------|--|--|--|--------|---|--|--|--------|---|--|--|

|           |                                             |        |  |  |  |        |   |  |  |        |   |  |  |

| 1.1       | Individuazione delle soluzioni              |        |  |  |  |        |   |  |  |        |   |  |  |

|           | tecnologiche in termini di materiali e      |        |  |  |  |        |   |  |  |        |   |  |  |

|           | processi                                    |        |  |  |  |        |   |  |  |        |   |  |  |

| 1.2       | Acquisizione dell'attrezzatura necessaria   |        |  |  |  |        |   |  |  |        |   |  |  |

|           | per il bonding e sviluppo della tecnologia. |        |  |  |  |        |   |  |  |        |   |  |  |

| 1.3       | Messa a punto del processo di taglio per la |        |  |  |  |        |   |  |  |        |   |  |  |

|           | separazione dei componenti dal wafer        |        |  |  |  |        |   |  |  |        |   |  |  |

| 1.4       | Individuazione e messa a punto delle        |        |  |  |  |        |   |  |  |        |   |  |  |

|           | procedure di "reworking"                    |        |  |  |  |        |   |  |  |        |   |  |  |

| 1.5       | Ottimizzazione del processo di              |        |  |  |  |        |   |  |  |        |   |  |  |

|           | allineamento e saldatura per l'assieme      |        |  |  |  |        |   |  |  |        |   |  |  |

|           | multiplo                                    |        |  |  |  |        |   |  |  |        |   |  |  |

| 1.6       | Realizzazione prima serie di prototipi A    |        |  |  |  |        |   |  |  |        |   |  |  |

|           | (cella 50x400 μm)                           |        |  |  |  |        |   |  |  |        |   |  |  |

| 1.7       | Realizzazione seconda serie di prototipi B  |        |  |  |  |        |   |  |  |        |   |  |  |

|           | (cella 50x300 µm)                           |        |  |  |  |        |   |  |  |        |   |  |  |

|           | , ,                                         |        |  |  |  |        | ı |  |  |        | ı |  |  |

| 2.1       | Ottimizzazione delle procedure finalizzata  |        |  |  |  |        |   |  |  |        |   |  |  |

|           | alla produzione di serie                    |        |  |  |  |        |   |  |  |        |   |  |  |

| 2.2       | Realizzazione della preserie                |        |  |  |  |        |   |  |  |        |   |  |  |

|           | *                                           |        |  |  |  |        |   |  |  |        |   |  |  |

Il progresso del progetto e' stato monitorato da una comitato di coordinamento paritetico (M.Caccia e L.Rossi (INFN) e A.M. Fiorello e M. Varasi (AMS)) che si e' riunito periodicamente.

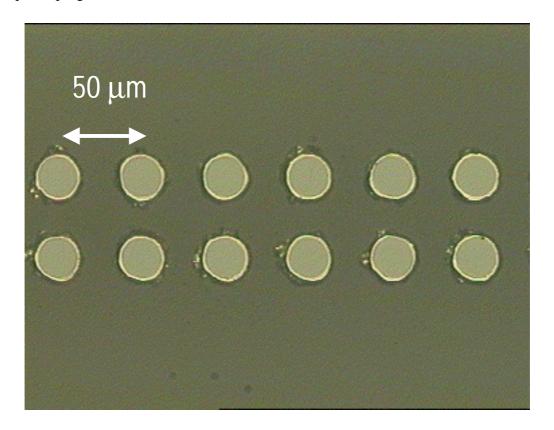

Dopo la messa a punto del processo litografico e di deposizione di indio si sono verificate le proprieta' elettriche ( $R\sim10~\Omega$ ) e meccaniche (stacco a trazione a 0.1g per bump) delle connessioni, entrambe sono risultate soddisfacenti.

Il rendimento della deposizione di bump e' stato subito buono (<0.01% bump mancanti), così come l' uniformita' di altezza (<0.5  $\mu$ m) e l'allineamento relativo dei due campioni .

L'altezza dei bump e' stata oggetto di ottimizzazione pur nell' ambito di un procedimento il piu' semplice possibile (a 1 sola maschera, per motivi di costi e rendimenti) passando da  $4-5~\mu m$  a  $7~\mu m$ .

I bump debbono essere almeno alti 7 μm perche' l'induzione tra segnali digitali dell'elettronica di front-end e il sensore dia effetti trascurabili.

In questa fase la deposizione dei bump e' stata fatta su wafer fino a 6" di diametro. L'operazione di flip-chip (cioe' la saldatura) e' stata fatta nella sezione INFN di Genova tramite un' apparecchiatura manuale (Finetec – Finplacer96) in attesa della macchina semiautomatica (Karl-Suss FC6) il cui acquisto, programmato in AMS nel quadro di questo programma di R&D, non era ancora stato concluso.

Questa figura illustra un assieme realizzato in vetro con bump al passo di  $50 \mu m$ , lo stesso che si deve usare per i rivelatori a pixel di ATLAS. I campioni in vetro sono stati realizzati per mettere a punto il processo e ottimizzare i parametri sia di deposizione di bump che di flip-chip.

Il passo successivo e' stato quello di realizzare assiemi singoli e multipli con sensori in silicio ed elettronica per poter ricavare i parametri di funzionamento di un modulo in condizioni operative.

A questo scopo sono stati utilizzati prototipi del rivelatore a pixel di ATLAS sia per i sensori che per l'elettronica di lettura.

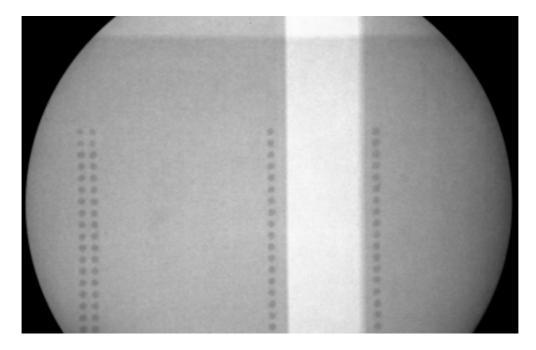

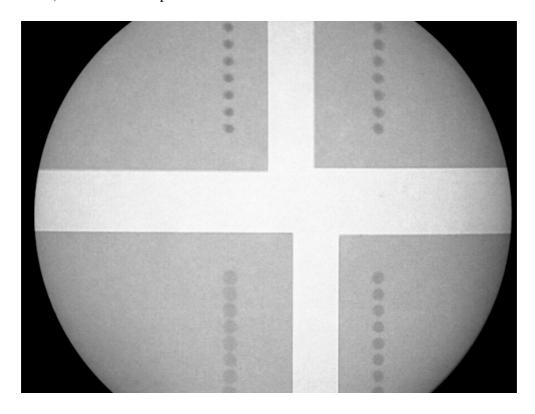

Le caratteristiche di questi assiemi sono state studiate mediante microradiografie a raggi X e con test di laboratorio.

Nella figura soprastante si vede la microradiografia di un dettaglio del modulo pixel che si trova al confine tra due chip di elettronica. Si riconoscono i bumps (macchie scure in sequenza), il bordo di due chip di lettura (zona grigia piu' scura) e il bordo del sensore (line orizzontale in alto). Tramite immagini come queste si possono vedere molti tipi di difetti nella deposizione di bumps o nella loro saldatura.

L'immagine in basso illustra un difetto: bumps troppo schiacciati ( e quindi possibili corti circuiti) al bordo del chip in basso a sinistra

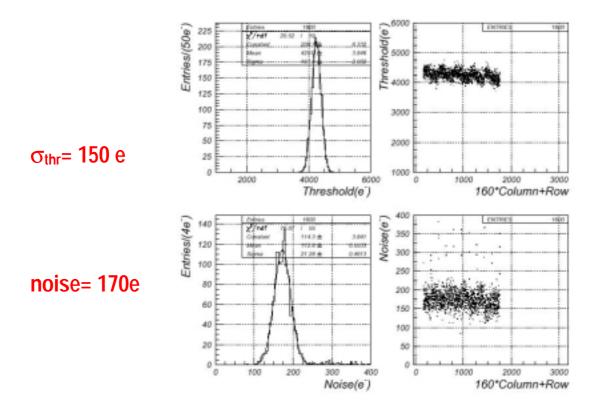

Le prove di laboratorio hanno consentito di misurare i parametri principali di un modulo pixel, cioe' la soglia di lavoro (e la sua dispersione) e il rumore.

I valori ottenuti sono indicati nella figura che segue e sono ritenuti soddisfacenti per il funzionamento a LHC.

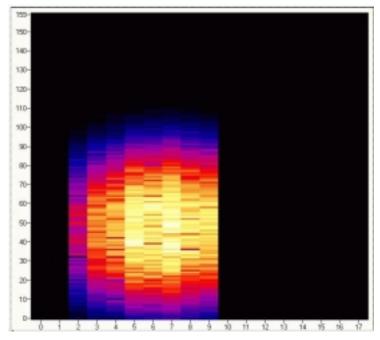

Infine la figura a fianco rappresenta il conteggio accumulato su un sensore quando questo e' irraggiato da una sorgente di <sup>109</sup>Cd, la quale emette raggi-X da 22 keV.

La sorgente investe le righe 2-9 e le colonne 0-90, la zona piu' chiara e' quella con piu' alti conteggi.

La figura mostra che tutti i pixel investiti dalla sorgente sono attivi, che il rumore di fondo e' molto basso (non ci sono hits spuri fuori dalla regione irraggiata) e che la soglia di funzionamento e' effettivamente bassa (22 keV corrispondono a circa 6000 e').

# <u>Rivelatori di particelle ionizzanti a microelettrodi in gas (MSGC)</u> (ditta LABEN)

L'obiettivo fondamentale del programma 5% MSGC e' stato lo sviluppo della tecnologia necessaria alla produzione di rivelatori del tipo MSGC/MGC di grande area (fino a  $25x10 \text{ cm}^2$ ) e la ingegnerizzazione della produzione di questi rivelatori su vasta scala (fino a 10.000 unita), con costi unitari contenuti.

A tale scopo Laben, industria italiana ad alta tecnologia del gruppo Finmeccanica , ha costituito con CETEV un team industriale avente come capofila Laben con il compito di curare e coordinare i rapporti fra le singole realta' industriali e l'INFN.

L'attivita' si e' sviluppata in due fasi distinte , gia' previste in sede di stesura del progetto:

- 1. Messa a punto della tecnologia del sensore (rivelatori a microelettrodi in gas segmentati in strisce miniaturizzate) capace di operare in presenza di elevate dosi di radiazione e di eventi ad alta ionizzazione specifica

- 2. Ingegnerizzaione della produzione su larga scala attraverso la realizzazione di una preserie di ~100 rivelatori MSGC per qualificare i processi produttivi, verificare le rese e quantificare i costi unitari.

#### I- Definizione della tecnologia (1997-1998) :

Gli ingredienti tecnologici fondamentali da sviluppare per rendere la tecnologia MSGC compatibile con la sperimentazione alle nuove macchine acceleratici erano;

- 1) capacita' di realizzazione di sensori di grande area su substrati sottili

- 2) trattamento della superficie del substrato per evitare fenomeni di instabilita'

- 3) passivazione di tutti gli spigoli catodici e discontinuita' per garantire un buon funzionamento ad alto guadagno.

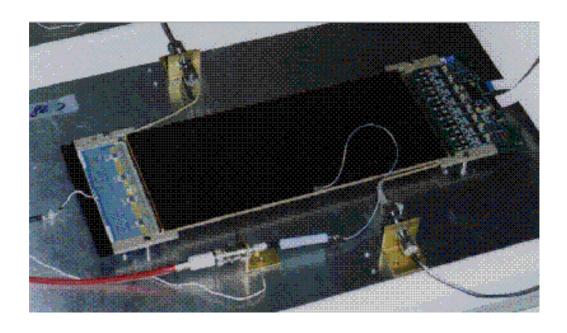

Rivelatori MSGC di grande area sono stati realizzati presso la CETEV di Carsoli utilizzando tecniche 'dry" (ion etching e sputtering). Si tratta dei piu' grandi rivelatori mai costruiti al mondo nello spessore di 0.3 mm.La resa iniziale e' stata di circa il 50%. Il substrato e' stato assemblato in laboratorio con la elettronica di lettura e provato sul banco con risultati piu' che soddisfacenti (fig. 1).

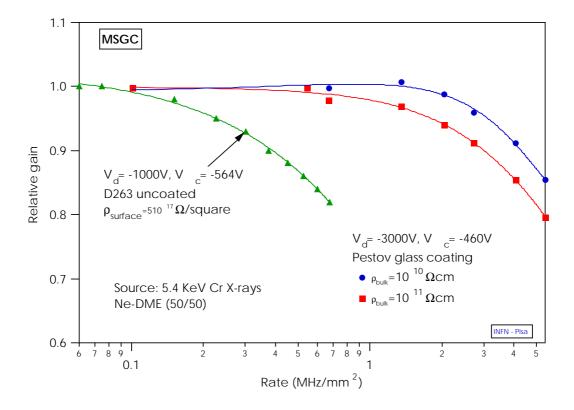

Uno dei problemi piu' critici per il buon funzionamento dei rivelatori MSGC in ambienti a flusso elevato di radiazione e' la necessita' di un trattamento della superficie con materiali provvisti di una piccola, ma non nulla, conducibilita' elettrica per drenare le cariche che eventualmente finiscano sul vetro. A questo proposito e' stato sviluppata presso la CETEV una tecnica di sputtering di un sottile ( $\sim 1~\mu m$ ) strato di materiale semiconduttore ( vetro Schott 8900) in grado di conferire al substrato una conducibilita' superficiale di tipo elettronico del valore appropriato ( $\sim 10^{15}~o hm/quadrato$ ).

La fig. 2 mostra il guadagno in capacita' di conteggio ottenuto utilizzando substrati trattati, rispetto a substrati privi di coating.

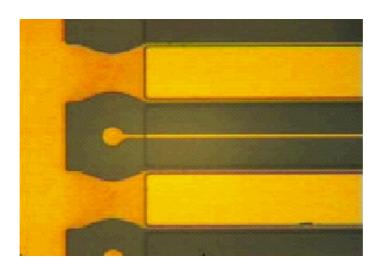

Indubbiamente lo sviluppo tecnogico piu' importante e' stato la messa a punto della tecnica di passivazione degli elettrodi critici. Si tratta di una tecnica multistrato che richiede quindi capacita' di allineamento con precisone submicrometrica su grandi aree.

Nell'ambito del progetto e' stata messa a punto una tecnologia innovativa detta di "passivazione avanzata" che consiste nel coprire tutte le strutture critiche con un sottile strato di materiale dielettrico (polyimide) e la sua successiva definizione con tecniche fotolitografiche.

Questo specifico trattamento del substrato ha conferito ai rivelatori MSGC sviluppati nell'ambito del progetto 5% caratteristiche tecniche altamente competitive che li hanno resi di fatto il punto di riferimento a livello mondiale. La fig. 3 mostra una dettaglio del rivelatore evidenziante il procedimento di protezione con la tecnica standard e quella "avanzata".

Figura 3

# Front-end, lettura e trigger per lo spettrometro u di ATLAS (ditta CAEN)

Il progetto ha per scopo la realizzazione del sistema di trigger di primo livello di muoni , della parte centrale("barrel") dell'esperimento ATLAS.

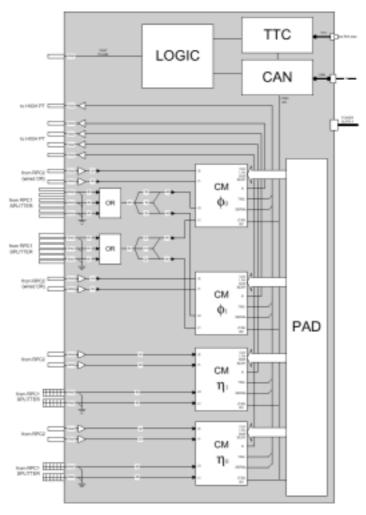

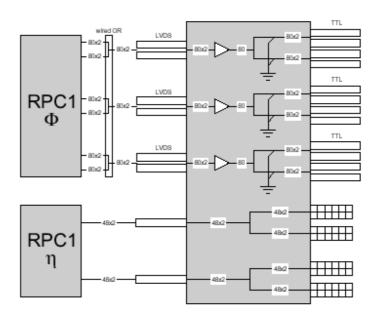

Il sistema di trigger si basa sulla lettura di segnali provenienti da un rivelatore dedicato, Resistive Plate Chamber (RPC) e sulla loro eleborazione in speciali processori locali, chiamati PADs, ubicati sul rivelatore stesso. I PADs sono di due tipi: quelli dedicati alla selezione di particelle con basso momento trasverso, Low Pt, e quelli dedicati alla selezione di particelle con alto momento trasverso, High Pt. Anche se fisicamente i due PADs sono uguali, dal punto di vista logico svolgono funzioni diverse. Nel sistema di trigger ci sono in totale circa 400 processori di Low Pt e altrettanti High. Il PAD di Low Pt (fig.1) trasferice i risultati della propria elaborazione a quello di High

Figure 1 - Schema a blocchi della Low Pt PAD

Pt (fig.2), che elabora l'informazione locale complessiva di trigger e la trasferisce, attraverso un link ottico, a dei moduli di elettronica ubicati in sala di controllo. I moduli sono: il Ricevitore Ottico, la Logica di Settore ed il Read-Out Driver (ROD). Ogni terna

Figure 2 - Schema a blocchi della high Pt PAD

di tali moduli mette insieme l'informazione di trigger di 1/32 dell'apparato e la trasferisce poi al Processore Centrale di trigger ubicato nella stessa sala di controllo.

L'algoritmo di trigger e gran parte delle operazioni ad esso accessorie sono gestite dal chip Matrice di Coincidenze (CM), che dovra' essere appositamente sviluppato. Esso sara' realizzato in tecnologia "deep submicron" 0.18 µm e lavorera' ad una frequenza di 320 MHz. Ogni processore PAD ospitera' quattro chip CM.

Questo progetto ha avuto inizio a gennaio 1999, con alcuni mesi di ritardo rispetto al previsto, dovuto essenzialmente a due ragioni. Si e' visto, da calcoli sviluppati dalla collaborazione Atlas, che, contrariamente a quanto previsto in precedenza, l'elettronica

impiegata sull'apparato dovra' essere di tipo resistente alle radiazioni, sino ad un valore stimato di 10 krad, e non dovra' essere sensibile al danneggiamento provocato dai neutroni. Da studi effettuati, si e' stabilito che tale problema puo' essere affrontato mediante l'impiego di circuiti integrati sviluppati in tecnologia di tipo "deep-submicron". La disponibilita' commerciale di tali processi e delle librerie digitali per lo sviluppo dei circuiti integrati si e' avuta tardi.

In secondo luogo si e' atteso che apparissero sul mercato nuove soluzioni tecniche per la parte del progetto che riguarda la trasmissione dei dati di trigger e read-out. Tali soluzioni consentono di unificare in una sola connessione la trasmissione dei dati di trigger e quelli di read-out, contrariamente a quanto previsto precedentemente nel progetto.

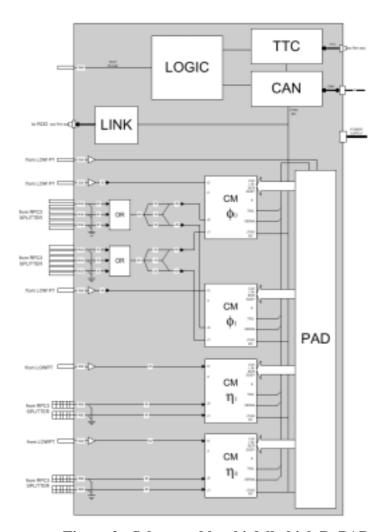

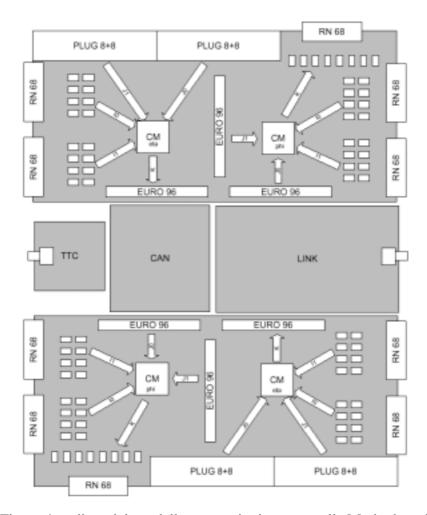

All'inizio del 1999 l'attivita' e' consistita, essenzialmente, nello studio e realizzazione dal solo punto di vista meccanico di un prototipo di Logica Locale contenente quattro matrici di coincidenza (contenitore, connessioni di ingresso e uscita, possibili lay-out, dimensioni delle schede, dissipazione termica, ecc.). Il completamento globale del progetto e' proseguito nei mesi successivi. In esso si e' tenuto conto di alcune modifiche al sistema di cablaggio e distribuzione dei signali, con l'introduzione, tra il front-end ed il trigger, di una scheda di splitter dei segnali stessi (fig.3). La box, oltre agli elementi di cui sopra,

Figura 3: schema a blocchi dello Splitter

dovra' alloggiare tutti i circuiti di somma dei segnali, una scheda di gestione dei bus seriali di servizio I2C, CAN e JTAG, la scheda di tramissione ottica dei dati, ed il sistema di ricezione e distribuzione delle temporizzazioni, TTCRX (fig.4). E' previsto anche il raffreddamento della box, mediante una serpentina all'interno della quale circola del liquido. L'attività svolta si è divisa in due fasi.

Nella prima si pensato alla raccolta e stesura organica delle informazioni, alla generazione di documenti che evidenziano schemi a blocchi funzionali, problematiche di interconnessione, scelta dei componenti e stima delle dissipazioni.

Figure 4 - disposizione delle connessioni esterne sulla Motherboard PAD

Nella seconda fase si è sviluppato un prototipo in grado di simulare gli ingombri, la connettività e il comportamento termico. Per quel che riguarda le specifiche del progetto, dal canto suo, l'INFN, ha modificato in parte il progetto del trigger, per aumentarne la robustezza verso i falsi trigger che potrebbero essere generati dal fondo di bassa energia presente nella caverna dove l'esperimento e' alloggiato. Si e' pure introdotta, nel sistema, una scheda di splitter e distribuzione dei segnali tra il front-end ed il trigger, che consente un piu' razionale cablaggio del sistema stesso.

# Alimentatori per alte tensioni continue (ditta CAEN)

Lo scopo di questo programma e' quello di sviluppare un sistema di generazione e regolazione di alte tensioni continue di tipo modulare, affidabile, di costi affrontabili e adatto all'utilizzo nelle condizioni operative degli esperimenti a LHC, cioe' in presenza di elevati flussi neutronici e di elevati campi magnetici.

Per verificare la flessibilita' del sistema, cioe' la sua capacita' di essere utilizzato per un ampio spettro di rivelatori, si e' scelto di studiarne l'applicazione concreta a due tipi di rivelatore molto diversi tra loro: le camere a deriva per  $\mu$  ed i rivelatori a microstrip in gas dell'esperimento CMS.

Quanto segue descrive lo studio preliminare sulla struttura e le caratteristiche del sistema, approvate dal Comitato Paritetico il 29 marzo 1999, nonche' le indicazioni ricavate dal test su un prototipo funzionale.

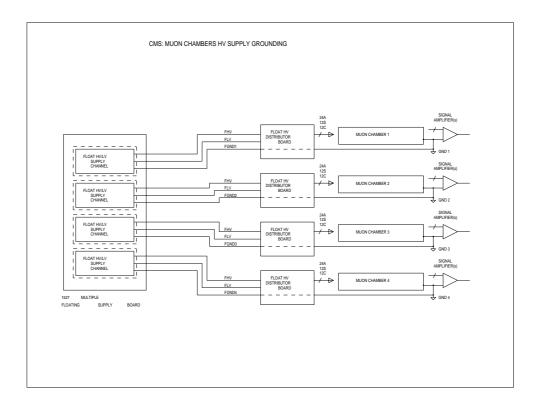

# Applicazione per il rivelatore a deriva per µ

#### La struttura del rivelatore

La struttura del rivelatore di  $\mu$  dell'esperimento CMS, decisa dalla collaborazione, e' la seguente:

- 250 Camere distribuite su 5 Ruote in 4 Stazioni coassiali al fascio, denominate MB1, MB2, MB3 e MB4.

- le camere sono costituite da unita' funzionalmente indipendenti, chiamate SuperLayer (SL):

- le camere nelle stazioni MB1, MB2, MB3 sono equipaggiate con 3 SL, due orientate con i fili sensibili paralleli ai fasci (SL  $\phi$ ) ed uno in direzione perpendicolare (SL  $\theta$ );

- le camere MB4 sono equipaggiate con due SL  $\phi$  e non contengono SL  $\theta$ ;

- ciascun SL e' formato da 4 piani sensibili (Layer), costituiti da celle a deriva; le celle di ciascun Layer sono sfalsate di mezza cella rispetto ai Layer adiacenti;

- all'interno di ciascuna cella il campo elettrico di deriva ed amplificazione e' formato con tre elettrodi :

- un filo assiale a tensione anodica +3.9 kV max (W)

- due striscie ad esso affacciate lungo le pareti superiore e inferiore per il controllo della uniformita' del campo di deriva a +1.9 kV max (S)

- due striscie catodiche lungo le pareti laterali a –1.9 kV max

La particolare struttura dei SL e' legata alla possibilita' di usare i SL stessi come sorgente di trigger; in tale struttura l'assenza o il malfunzionamento di un SL limita l'efficienza e la precisione spaziale, ma non impedisce il trigger che puo' ancora essere fornito da 3 soli Layer su 4.

Di conseguenza l'alimentazione delle HV per le camere segue una distribuzione per Layer, in modo da preservare la capacita' di trigger in caso di cattivo funzionamento di una particolare linea di HV.

I limiti di funzionamento del primo prototipo di rivelatore in scala reale hanno mostrato come sia importante, per l'integrita' delle celle, che la differenza di tensione tra elettrodi W e S in ogni cella non superi il valore di 1900÷2000 V. Per tale ragione il sistema di distribuzione delle HV deve prevedere una protezione automatica hardware contro il superamento accidentale di questo limite.

La tensione anodica, che determina l'amplificazione delle cariche attorno al filo, e' senz'altro il parametro piu' critico del sistema. L'esperienza concreta su un rivelatore reale ha evidenziato l'utilita' di avere per questa tensione una granularita' di distribuzione piu' fine. Come compromesso tra questa esigenza e quella di contenere i costi del sistema si e' scelto di raddoppiare le linee di alimentazione anodica rispetto alle altre.

Il rivelatore e' per forza di cose distribuito in un volume di ferro molto esteso ove la qualita' del riferimento di massa non e' garantita. Cio' ha consigliato di prevedere le singole camere isolate dal giogo del magnete di CMS, implicando che le alimentazioni sia di bassa tensione sia di alta tensione abbiano a loro volta riferimento flottante.

La struttura metallica stessa delle camere e' il "punto di massa " per elezione sia delle alimentazioni sia dei segnali. Di conseguenza l'albero di distribuzione per le tensioni di alimentazione deve evitare accoppiamenti deleteri tra le camere e con il resto dell'apparato, attraverso loop delle connessioni e in particolare di massa.

#### Localizzazione del sistema

Riguardo alla localizzazione del sistema di generazione e distribuzione delle alte tensioni alle camere, si e' dovuto tenere conto di alcuni vincoli e situazioni caratteristici dell' esperimento CMS:

- Ridotta disponibilita' di spazio nella sala controllo principale adiacente alla caverna con accessibilita' continua

- Disponibilita' di spazio sulle "balconate" adiacenti la superficie esterna del ferro con accessibilita' programmata da definire (5÷10 volte l'anno)

- Campo magnetico disperso sulle balconate dell'ordine di 1 kGauss

- Livello di flusso neutronico sulle balconate sino a 20 Hz/cm2 per neutroni di energia superiore a 20 MeV alla massima luminosita' dell'acceleratore, pari a una fluenza di ~ 10<sup>9</sup> n/cm<sup>2</sup> in 10 anni di operazione di LHC (~5 x 10<sup>7</sup> sec)

- Scarsa dose integrata sulle balconate pari a circa 40 rad nelle stesse condizioni di operazione.

La disponibilità di spazio sulle balconate in condizioni ambientali e di accessibilità accettabili, anche se non ideali, hanno suggerito di articolare la struttura del sistema di alimentazione HV, separando le funzioni di generazione delle tensioni e la maggior parte di quelle di programmazione e controllo dalle funzioni di regolazione e lettura di tensioni e correnti.

. Nella Sala Controllo, dove il flusso neutronico ed il campo magnetico sono trascurabili, troveranno alloggiamento le prime, mentre le seconde saranno posizionate

sulle balconate. Di conseguenza solo per queste si dovra' tener conto in fase di progetto delle difficili condizioni ambientali.

#### Gli Obiettivi

In relazione alle considerazioni sviluppate sopra, si sono definite le caratteristiche da realizzare per il sistema :

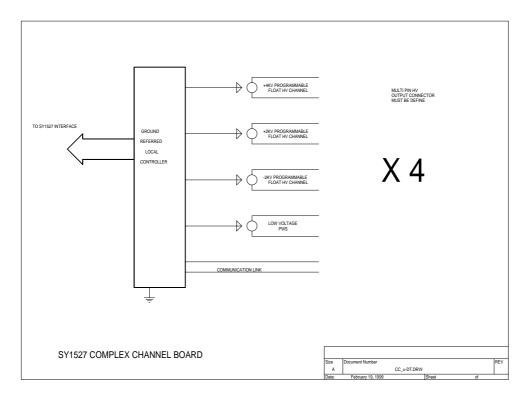

- Adozione del sistema SY1527, gia' sviluppato e pronto ad entrare sul mercato, come main frame (MF) da alloggiare in sala controllo, con le funzioni di generazione delle tensioni primarie, di intelligenza, controllo e interfacciamento al sistema generale di controllo di CMS.

- Definizione delle caratteristiche di un modulo primario (PCM) dedicato alle funzioni specifiche di generazione delle tensioni primarie, corredato dell'intelligenza adeguata a gestire le funzioni di controllo per moduli di regolazione periferici, e la relativa raccolta dei dati di lettura per tensioni e correnti. Un PCM dovra' essere in grado di fornire le tre alte tensioni (+4 kV, +2 kV, -2 kV), la bassa tensione (+12 V) e una connessione seriale di comunicazione con masse indipendenti e flottanti per quattro moduli periferici.

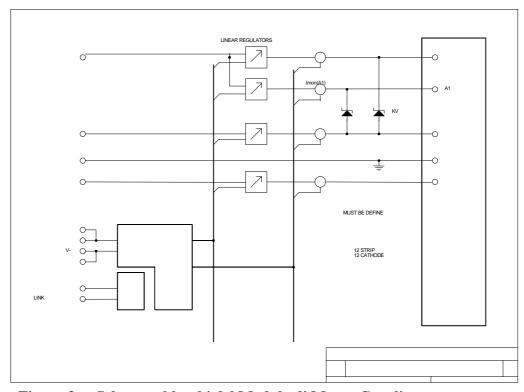

- Definizione delle caratteristiche di un Macro Canale (MC) direttamente collegato alle camere. Questo, per adeguarsi al rapporto di granularita' sopra definito, e' costituito da 2 canali anodici (W) indipendenti, regolabili da 0 a +4 kV, da 1 canale di Strip (S) regolabile da 0 a +2 kV e da 1 canale catodico (C) regolabile da 0 a -2 kV. I due canali W sono asserviti al canale S in modo da garantire che la ddp tra essi non superi mai i 2 kV. La potenza fornita da ciascun MC deve permettere di alimentare un intero layer di camera indipendentemente dalle dimensioni (MB1 ..... MB4);

- Definizione delle caratteristiche di un modulo periferico (MCM) in grado di alloggiare 12 Macro Canali con massa comune flottante, corredato dal minimo di intelligenza necessaria all'esecuzione dei comandi di stato e regolazione, alla lettura di correnti e tensioni e ad interfacciarsi con la linea di comunicazione con il PCM. Tutti i dispositivi costituenti un MCM devono essere in grado di mantenere la loro funzionalita' nelle condizioni ambientali delle balconate ove saranno situati.

Da una stima preliminare degli spazi disponibili nell'esperimento e dei costi globali del sistema di HV, si sono adottate le seguente ipotesi di partenza per il sistema di distribuzione:

- moduli primari PCM in grado di alloggiare 4 gruppi (PC) indipendenti di tensioni, ciascuno in grado di alimentare una camera completa. Le dimensioni dei moduli devono permettere l'alloggiamento di 8 moduli in un crate MainFrame;

- moduli secondari MCM, ciascuno alimentato da un gruppo PC, alloggiati in crate di dimensioni massime 8U. In ciascun crate devono alloggiare almeno 8 MCM;

Lo schema di fig. 1 chiarisce la connettivita' basilare di 1 modulo PC verso 4 moduli MC e le relative quattro camere

Figura 1 - Connessioni tra moduli PC e MC

# Test preliminari

Prima ancora di conoscere esattamente le condizioni di flusso neutronico e di dose presenti nella zona di localizzazione dei moduli di macrocanali, la ditta CAEN ha condotto una campagna di test su numerosi componenti circuitali.

I risultati sono riportati nei documenti CAEN: "Risultati dei test preliminari di irraggiamento con dosi di 20Krad, 1Mrad, 3Mrad" e "Risultati dei test preliminari di bombardamento neutronico con fluenze di: $10^{12}$ n/cm²,  $10^{13}$  n/cm²,  $2*10^{13}$  n/cm² ". Tali test hanno consentito una prima selezione di componenti potenzialmente piu' adatti al progetto.

# Il Prototipo funzionale

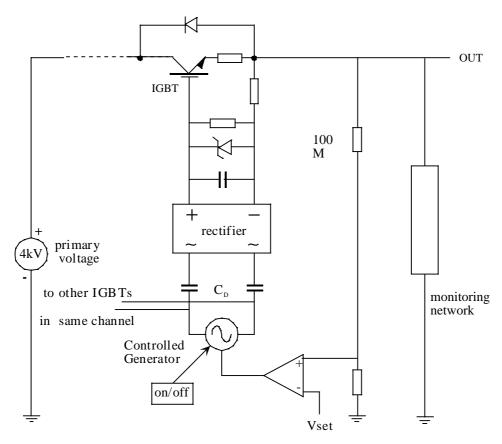

Allo scopo di verificare la validita' e praticabilita' di alcune soluzioni circuitali, e' stato studiato e realizzato dalla ditta CAEN un prototipo funzionale per la generazione e regolazione delle tensioni richieste. Tale prototipo consiste di un modulo primario di generazione delle tensioni primarie interfacciato da un lato a un Main Frame di controllo SY1527, dall'altro a quattro moduli ciascuno equipaggiato con le funzioni di un macro canale, dotato di 4 canali anodici anziche' due. Le figure 2 e 3 rappresentano gli schemi a blocchi dei due moduli

Figura 2 - Schema a blocchi del Modulo di Canali Primari

Figura 3 - Schema a blocchi del Modulo di Macro Canali

Le caratteristiche essenziali di ciascun canale sono evidenziate nella successiva figura 4.

Figura 4 - Schema di principio del canale anodico

Il prototipo funzionale e' stato ricevuto dall'INFN a fine ottobre 1998 ed e' stato sottoposto a test sino a fine gennaio 1999. In questo periodo ha mostrato problemi erratici di comunicazione, di stabilita' e di elevati offset nelle letture in tensione e corrente, nonche' di affidabilita' nelle connessioni. Le cause di tali problemi sono state via via corrette da CAEN.

Questo processo ha portato alla introduzione nel disegno di varie modifiche:

- sostituzione dei diodi di protezione e proposta di sostituzione con VDR

- ottimizzazione dei circuiti di lettura e monitor e adeguamento del layout nei circuiti stampati.

- Sostituzione di alcuni tipi di connettori e perfezionamento dei circuiti di comunicazione e ridimensionamento dell'alimentatore flottante di bassa tensione

### Il Prototipo finale

L'esperienza e le indicazioni tratte dal test del prototipo funzionale hanno fornito la base per orientare il progetto e l'ingegnerizzazione del prototipo finale.

La struttura generale del sistema e' rimasta invariata, come pure le linee generali del singolo canale come descritti negli schemi a blocchi precedenti.

I diodi di protezione sono stati sostituiti con dispositivi VDR con minore corrente di perdita, e' stata studiata una ottimizzazione dei circuiti di monitor e comunicazione e del loro layout ed e' infine stato avviato lo studio di ingegnerizzazione dei due moduli PCM e MCM secondo la granularita' prima descritta.

La consegna di un prototipo per tipo di modulo e' stata programmata per agosto 1999.

### Applicazione per i rivelatori a microstrip in gas (MSGC)

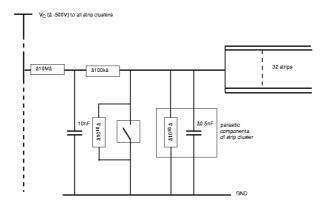

Scopo fondamentale del progetto 5% HV per le Microstrip Gas Chambers e' stato lo sviluppo di un sistema di alte tensioni con la modularita' e la funzionalita' necessaria e con costi unitari per canale che siano una frazione piccola rispetto al costo del rivelatore stesso (vedi figura 1)

Figura 1

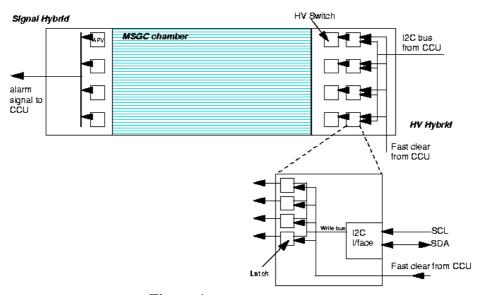

Il problema principale da risolvere nella prima fase del progetto (1997-1998) era quello del controllo delle alte tensioni in caso di scarica del rivelatore. Per ridurre la quantita' di carica disponibile per sostenere la scarica, le strips catodiche sono raggruppate in gruppi e ciascun gruppo e' connesso ad una tensione di alimentazione comune (~520 V)

attraverso un resistenza di limitazione. Quando una sovracorrente in un gruppo viene rivelata e' necessario rimuovere selettivamente la tensione al gruppo. Questo schema (vedi figura 2), richiede la realizzazione di ~200.000 switch ad alta tensione.

Figura 2

Nella prima fase si e' sviluppato un prototipo di ibrido per le switch con le funzionalita' richieste, ma in tecnologia non rad-hard ed il relativo canale di alta tensione. Sono stati prodotti 100 esemplari di ibrido in tecnologia PCB standard che sono stati testati e verificati avere le caratteristiche di sensibilita' e velocita' richieste. La fase successiva del lavoro richiede lo sviluppo dell'ibrido in tecnologie rad-hard e di un modulo completo per le alte tensioni con modularita' elevata (almeno 16 canali per modulo) per abbattere i costi unitari.

# Sviluppo dell'elettronica di lettura per una camera a proiezione temporale ad argon liquido (ICARUS) (ditta CAEN)

Nell'esperimento Icarus, il sistema di lettura dei dati del primo modulo da 600 ton riguarderà 54.272 canali. Di ciascun canale sarà necessario memorizzare la coordinata temporale e la forma del segnale per un periodo di tempo sufficientemente lungo per una corretta analisi, da effettuarsi successivamente.

Nella **proposta iniziale** di esperimento, il sistema di read out era strutturato come segue:

-amplificatore di front end; -multiplexer analogico; -convertitore AD a 10bit; -estrattore del segnale di traccia; -buffer digitale.

Amplificatore di front end: L'amplificatore di front end doveva essere alloggiato all'esterno del criostato in crates prossimi alle flange che supportano i connettori di uscita, al fine di minimizzare il rumore serie del canale e le difficoltà di cablaggio. Si proponeva di realizzare un amplificatore VLSI in tecnologia CMOS con elemento d'ingresso jFet, che permetteva di ottenere un rapporto segnale rumore adeguato. La soluzione molto compatta (2 canali per integrato) consentiva anche di ottenere un'alta affidabilità per il ridotto uso di componentistica discreta.

**Multiplexer analogico :** Al fine di minimizzare il numero di connessioni verso la parte di elaborazione digitale dei dati, si pensava di raggruppare i canali in insiemi di 16, con la tecnica del multiplexer analogico. Un sistema che scandisse i singoli canali, a valle dell'amplificatore, con periodo di 25 ns, avrebbe permesso poi di convertire i 16 canali con un solo ADC, campionando ciascun canale ogni 25 ns•16 =400 ns, corrispondenti ad una lunghezza di deriva di circa 500 µm, compatibile con la risoluzione dell'apparato.

Convertitore AD a 10 bit: Il convertitore a 10 bit, dopo una prima valutazione dell'ADC del progetto FERMI, si era deciso che dovesse essere di tipo commerciale, essendo la tecnologia ormai largamente diffusa, a causa dello sviluppo di dispositivi di largo consumo che richiedono conversioni ad alta velocità e risoluzione media (10 bit).

**Estrattore del segnale :** In base all'esperienza maturata nell'analisi dei segnali del prototipo da 3 ton, si era completamente descritto in VHDL, un sistema digitale, chiamato Daedalus, in grado di trattare i segnali di sedici fili adiacenti ed di estrarne il segnale di traccia, al fine di comandare la registrazione di un gruppo di canali, nel buffer digitale, solamente in presenza di tracce.

**Buffer digitale :** Si proponeva la realizzazione di un sistema multibuffer da associare a ciascun canale, che selezionasse solo l'intervallo di tempo in cui c'è segnale e che ne effettuasse la registrazione associata al tempo assoluto in cui è riconosciuto l'evento. I moduli, realizzati in standard VME, dovevano servire gruppi di almeno 16 canali.

### Previsioni sullo sviluppo del progetto

Nella proposta iniziale il progetto veniva diviso in *tre fasi* che, parzialmente, si sovrapponevano temporalmente:

- -sviluppo dei **componenti base** (Amplificatore, Multiplexer, Dedalus, ADC), da terminare entro 1 anno dall'inizio del finanziamento 5%;

- -progetto esecutivo entro 1 anno;

- -costruzione di 1000 canali pilota, entro 2 anni.

#### Consuntivo e attività svolte fino all'estate del 1999.

Alla fine del 1996 è iniziato lo sviluppo del progetto in collaborazione con la società CAEN spa e di seguito vengono esposte le evoluzioni tecnologiche e lo stato del progetto stesso.

## Componenti analogiche integrate

Alla fine del 1997 erano stati sviluppati, in stretta collaborazione con la CAEN spa, sia l'amplificatore VLSI in tecnologia BiCMOS presso la fonderia AMS (Austria MikroSysteme), che il multiplexer a 16 ingressi. Tuttavia la disponibilità creatasi sul mercato di ADC e multiplexer a costo molto basso, ha indicato che la soluzione migliore nei termini di rapporto qualità costo non era quella dell'uso di un solo ADC e di un solo multiplexer, bensì quella di utilizzare una struttuta leggermente più complessa. Si è deciso quindi di utilizzare due ADC con multiplexer commerciale a 8 ingressi e di mescolare le uscite digitali con un multiplexer digitale a due ingressi da 10 bit. Pur essendo i prototipi di multiplexer realizzati attraverso AMS perfettamente entro le specifiche la soluzione più conveniente si è dimostrata quella commerciale. Per quanto riguarda gli amplificatori invece è stata decisa la loro produzione attraverso il programma di Small Production di Europractice.

#### Moduli analogici di lettura

Una prima versione di modulo analogico, a 16 canali, è stata sviluppata da CAEN spa in standard NIM. Verificate le prestazioni in termini di S/N, linearità integrale e differenziale, i moduli finali sono stati sviluppati in standard meccanico VME, adottando per essi un bus disegnato ad hoc. La soluzione VME ha permesso di realizzare moduli analogici a 32 canali.

# Componenti digitali integrate

Il componente Daedalus è stato realizzato, in stretta collaborazione con CAEN spa, in tecnologia CMOS 0.7 µm presso ES2, alla fine del 1997. Con tale tecnologia era stato possibile integrare 4 canali per integrato. Con tale componente, vedi sotto, erano stati realizzati i primi moduli digitali VME a 16 canali. Il cambiamento di strategia industriale di ES2, acquisita nel frattempo dalla statunitense ATMEL, ci ha poi imposto il

trasferimento del progetto ad altra tecnologia. La scelta è caduta sulla tecnologia Samsung, gate array  $0.5~\mu m$ , che ci ha vantaggiosamente permesso di integrare 16 canali in un singolo integrato.

#### Moduli digitali di lettura

La prima versione realizzata da CAEN spa, si basava sul Daedalus a 4 canali di ES2 e quindi il modulo serviva solamente 16 canali. La seconda versione sviluppata da CAEN spa attorno al componente Samsung, ha permesso di realizzare moduli VME a 32 canali.

#### Conclusioni

Al giugno del 1999 pertanto, erano state sviluppate (1997) ed erano disponibili tutte le componenti elettroniche di base (Daedalus e amplificatore BiCMOS). Nell'ambito del presente programma era già stata realizzata l'elettronica per 9920 canali.